Ian wrote:One idea ..

I wonder if we could simply capture all the data from the tilegen (in the emulator) and just send it to the real h/w for testing.

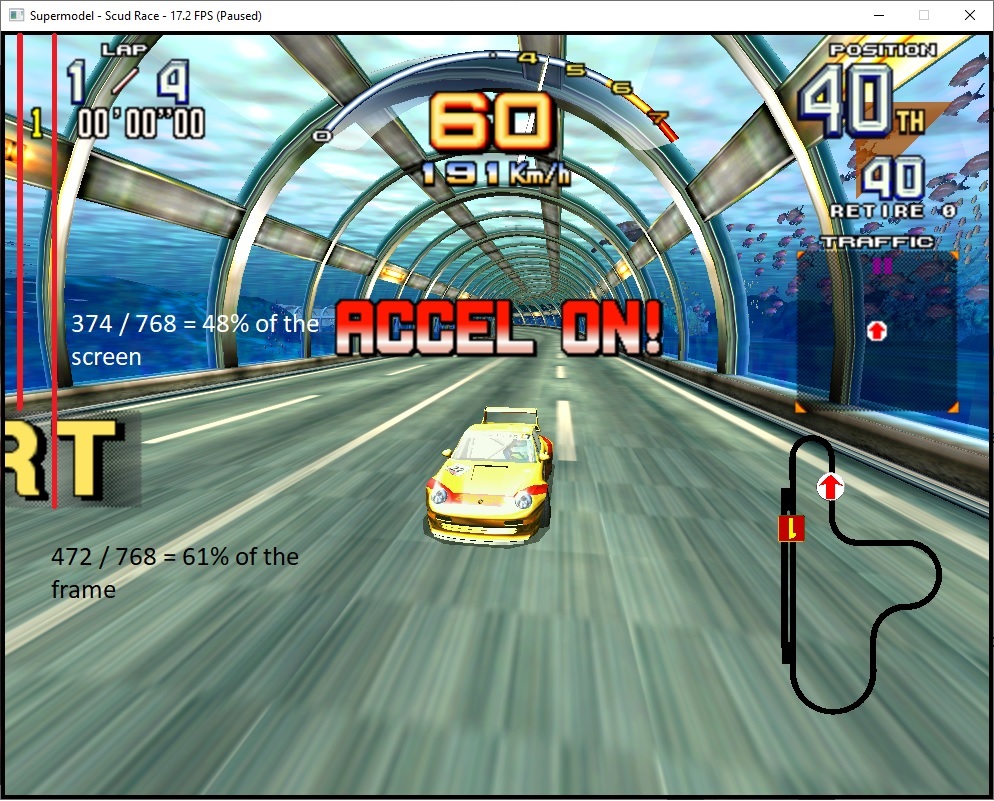

Ie freeze a frame of scud rolling start, then save the data.

If we did that we could eliminate any kind of timing problems. I think the tilegen is compatible between all the different h/w revisions? So could maybe test that that on a step 1.0 board?

This is a great idea! We should absolutely try this. It will reveal a lot.

One of my fears, mentioned in the comments atop Render2D.cpp, is that there is some sort of hardware register involved in setting up an offset. If so, it is being set through JTAG. I know for sure that JTAG is responsible for setting up timing registers that normally would be mapped to some address (as on System 24). I don't know exactly how, though. I just pump in data captured from VF3. However, model3man's information on boundary scan made me realize it should be possible to more diligently analyze how games program the JTAG and actually break down the bit stream into more meaningful parts. Worst case scenario, I could sit down and actually disassemble the entire boundary scan test code. It would take quite a while but we would probably get a really good picture of how the games program each specific chip, which in turn might allow us to isolate the bits that are fed to the tile generator and make sense of them. They almost certainly will map to the various hardware registers that Charles MacDonald has documented on the original System 24 board.