by Bart » Sun Dec 17, 2017 11:12 am

by Bart » Sun Dec 17, 2017 11:12 am

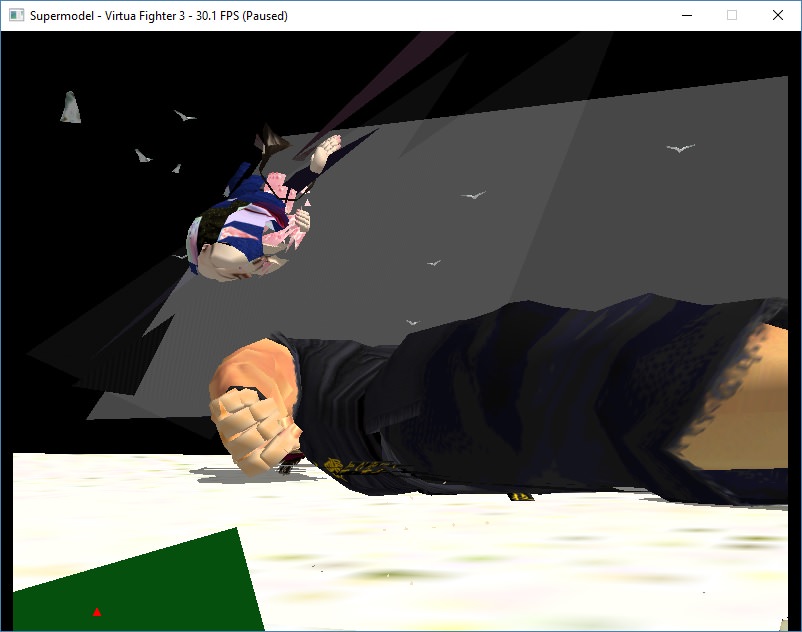

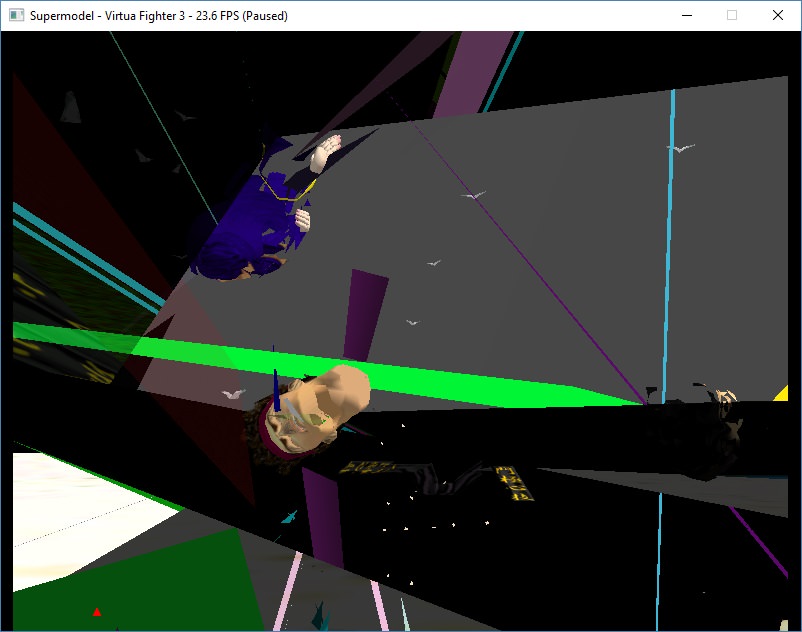

Timing definitely affects VF3 in that way. My timing changes also broke it.

I need to think about this some more tomorrow. My FV2 disassembly is actually on a work machine. The SDK refers to "culling RAM" and "ping pong RAM". We refer to these as culling RAM high/low. I think only one of these is swapped. I had once convinced myself that the games are performing a double-swap at the beginning, when initializing memory, so that they "know" exactly what is in which buffer when they start up. But reviewing the previous thread, I see that FV2 writes some data to 0x8cxxxxxx, flushes twice, and then writes more data there. This is during init only. Doesn't make a whole lot of sense anymore. I need to see all that code in context again.

Another test I could potentially do on the real hardware is write to 0x88000000 and see how long it takes the bit to flip. The code I've looked at, which measures the bit flip time, actually reads the "old" value immediately after the flush. Under my old hypothesis, that it was flipped at some specific point in the frame, this is fine. But if the flush actually triggers a swap immediately, the games should be saving this bit right before the flush.

Actually, come to think of it, maybe I should just test the calibration routine? I assume it will still work with garbage data in culling RAM. I could even probably duplicate the first few transfers that FV2 performs, just to set up the memory in a sensible fashion (really, just nulling out the viewports). This won't really confirm exactly what's going on but having some insight into the timing of all this would be super useful.

I wish we had time to create a test 3D scene that consisted only of two triangles, untextured, in poly RAM: one green, one red. I could then run some experiments, alternating frames to see when one gets rendered vs. the other... If someone could generate the necessary data (viewport, display list, culling node, transform matrix) in the next couple of days, I can try to write a program to do this...